Page 48 - bilgem-teknoloji-dergisi-7

P. 48

Serkan SEMİZ, H. Ercüment ZORLU FPGA Üzerinde Kanallaştırıcı Gerçeklenmesi

zayıflamadan 2 kanalda birden görünür olması amaçlanmış, 128 noktalık FFT’si alınır. Bunun için IP Core Generator ile silisyum verimliliği çok düşüktür [4]. Yüksek kapasiteli KAYNAKÇA

bu yüzden de kanallar arası uzaklığın 2 katı kadar fazla üretilen 128 örnek uzunluğuna sahip FFT bloğu FPGA’ler kullanarak ve DDC bloklarında ortak kaynak [1] W. Tuttlebee (ed.), Software Defined Radio: Enabling

örnekleme yapılmıştır; yani K D = 2 olmaktadır. kullanılmıştır. FFT bloğunun I ve Q çıkışları kanalların kullanımına yönelik iyileştirmeler yapılarak kanal sayısı bir Technologies. Chichester: John Wiley & Sons, 2002.

f = 30,72 MHz, K = 128 ve D = 64 seçilmesiyle karmaşık verilerini, endeks çıkışı ise o saat çevrimi içerisinde miktar artırılabilir. Daha yüksek kanal sayısının gerekli [2] L. Pucker, “Channelization techniques for software

s

f = 240 kHz ve f = 480 kHz olur. İki kanal arası üretilen verinin hangi kanala ait olduğunu ifade eder. olduğu durumlarda paralel DDC yöntemi yetersiz kalacaktır. defined radio,” Proc. SDR Forum Conf., Orlando, FL,

ç

u

uzaklığın yarısı ise 120 kHz’tir. Süzgecin kesim frekansı Çıkışlar faz düzeltme işleminden sonra son halini alır. Çok fazlı FFT tabanlı kanallaştırıcının silisyum verimliliği ise Nov. 2003:

seçilirken, kanal merkezine 120 kHz uzakta ve 96 kHz bant 240 kHz aralıklı olarak sıralanmış, 480 kS/s örnek hızına çok yüksektir [5]. Çok sayıda kanalın işlenmesinin gerektiği http://citeseerx.ist.psu.edu/viewdoc/download?doi=10.1

genişliğinde bir işaretin geldiği durum göz önünde sahip 128 kanal bu şekilde elde edilmiş olur. durumlarda önem kazanacak bu yapının kanallar arası .1.124.8152&rep=rep1&type=pdf

bulundurulmuş ve 168 kHz uygun görülmüştür. bağımsızlığı ise düşüktür. Ayrıca kanal sayısının 2N [3] Xilinx, Virtex–4 FPGA User Guide:

“Anahtarlama Matrisi” bloğunun görevi çok fazlı FFT

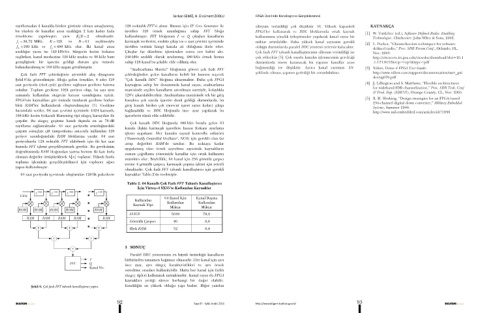

Çok fazlı FFT çekirdeğinin ayrıntılılı akış diyagramı çekirdeğinden gelen kanalların belirli bir kısmını seçerek şeklinde olması, yapının getirdiği bir zorunluluktur. http://www.xilinx.com/support/documentation/user_gui

Şekil 6’da gösterilmiştir. Bloğa gelen örnekler, 8 adet 128 “Çok Kanallı DDC” bloğuna aktarmaktır. Daha çok FPGA des/ug070.pdf

saat periyodu (clock cycle) gecikme sağlayan gecikme hattına kaynağına sahip bir donanımda kanal sayısı, anahtarlama [4] J. Lillington and S. Matthews, “Flexible architectures

sokulur. Toplam gecikme 1024 periyot olup, bu sayı aynı matrisinde seçilen kanalların artırılması suretiyle, kolaylıkla for wideband SDR channelisation,” Proc. SDR Tech. Conf

& Prod. Exp. (SDR’05), Orange County, CL, Nov. 2005.

zamanda kullanılan süzgecin katsayı uzunluğuna eşittir. 128’e çıkarılabilecektir. Anahtarlama matrisinde tek bir giriş

FPGA’nin kaynakları göz önünde tutularak gecikme hatları kanalına çok sayıda işaretin denk geldiği durumlarda, bu [5] R. H. Hosking, “Design strategies for an FPGA-based

blok RAM’ler kullanılarak oluşturulmuştur [3]. Gecikme giriş kanalı birden çok (mevcut işaret sayısı kadar) çıkışa 256-channel digital down converter,” Military Embedded

Systems, Summer 2006:

hattındaki veriler, 64 saat çevrimi içerisinde 1024 katsayılı, bağlanabilir ve DDC bloğunda ince ayar yapılarak bu http://www.mil-embedded.com/articles/id/?1898

168 kHz kesim frekanslı Hamming tipi süzgeç katsayıları ile işaretlerin tümü elde edilebilir.

çarpılır. Bu süzgeç geçirme bandı dışında en az 76 dB Çok kanallı DDC bloğunda 480 kS/s hızıyla gelen 64

zayıflama sağlamaktadır. 64 saat periyodu uzunluğundaki kanala ilişkin karmaşık işaretlere hassas frekans ayarlama

çarpım sonuçları çift tamponlama amacıyla kullanılan 128 işlemi uygulanır. Her kanalın sayısal kontrollü osilatörü

periyot uzunluğundaki RAM bloklarına yazılır. 64 saat (‘Numerically Controlled Oscillator’, NCO) için gerekli olan faz

periyodunda 128 noktalık FFT alabilmek için iki kat saat artışı değerleri RAM’de tutulur. Bu noktaya kadar

hızında FFT işlemi gerçekleştirmek gerekir. Bu gereksinim uygulanmış olan örnek seyreltme sayesinde kaynakların

doğrultusunda RAM bloğundan yazma hızının iki katı hızla zaman çoğullama yöntemiyle kanallar için ortak kullanımı

h

okunan değerler örtüştürülerek [ ] n toplanır. Yüksek hızda mümkün olur. Böylelikle, 64 kanal için 256 gömülü çarpıcı

toplama işleminin gerçekleştirilmesi için toplayıcı ağacı yerine 4 gömülü çarpıcı, karmaşık çırpma işlemi için yeterli

yapısı kullanılmıştır.

olmaktadır. Çok fazlı FFT tabanlı kanallaştırıcı için gerekli

64 saat periyodu içerisinde oluşturulan 128’lik paketlerin kaynaklar Tablo 2’de verilmiştir.

Tablo 2. 64 Kanallı Çok Fazlı FFT Tabanlı Kanallaştırıcı

İçin Virtex–4 SX35’te Kullanılan Kaynaklar

z − 128 z − 128 z − 128 z − 128

Giriş 64 Kanal İçin Kanal Başına

Kullanılan

Kaynak Tipi Kullanılan Kullanılan

Miktar

Miktar

ROM ROM ROM ROM ROM

SLICE 5048 78,9

RAM RAM RAM RAM RAM

Gömülü Çarpıcı 40 0,6

+ + + Blok RAM 52 0,8

+ +

+ 3 SONUÇ

Paralel DDC yönteminin en büyük üstünlüğü kanalların

I birbirinden tamamen bağımsız olmasıdır. Her kanal için ayrı

FFT Q ince ayar, ayrı süzgeç karakteristikleri ve ayrı örnek

Kanal No.

seyreltme oranları kullanılabilir. Hatta her kanal için farklı

süzgeç tipleri kullanmak mümkündür. Kanal sayısı da FPGA

kaynakları yettiği sürece herhangi bir değer olabilir.

Şekil 6. Çok fazlı FFT tabanlı kanallaştırıcı yapısı. Esnekliğin en yüksek olduğu yapı budur. Diğer yandan

92 Sayı 07 · Eylül-Aralık 2011 http://www.bilgem.tubitak.gov.tr/ 93