Page 47 - bilgem-teknoloji-dergisi-7

P. 47

Serkan SEMİZ, H. Ercüment ZORLU FPGA Üzerinde Kanallaştırıcı Gerçeklenmesi

indirilmesi aşamaları Şekil 2’de gösterilmiştir. Tablo 1. Tek Kanal DDC İçin Virtex–4 SX35’te Kullanılan

Çırpma CIC süzgeçler sadece toplayıcı ve fark alıcılardan Kaynaklar h n Ağırlıklandırma

[ ]

(a) oluşurlar; çarpıcı içermezler. Bu özellikleriyle yüksek örnek Kullanılan Kaynak Tipi Miktarı Fonksiyonu

seyreltmenin gerekli olduğu durumlarda daha çok tercih

edilirler. Ayrıca, farklı örnek seyreltme oranlarının kolayca SLICE 2061

yeniden ayarlanabilir olması önemli bir avantaj Gömülü Çarpıcı 10

f m f s 2 sağlamaktadır. Blok RAM 4 X [ ] n Ağırlıklandırılmış Veri

CIC süzgeçlerin geçirme bandı içerisindeki zayıflama

etkisini düzeltmek ve dolayısıyla, geçiş bandını düzleştirmek K Uzunluğunda

Bloklara

Süzme ve amacıyla çoğunlukla arkalarında birer adet CFIR 2.2 Çok Fazlı FFT Tabanlı Kanallaştırıcı Ayrılmış Veri

(b) (‘Compensation FIR’, Telafi Süzgeci) kullanılır. Bu süzgeçler

Örnek Çok fazlı FFT tabanlı kanallaştırıcıyı oluşturan bloklar

Seyreltme aynı zamanda örnek seyreltme işlemine de katkıda Şekil 4’te gösterilmiştir. Bu bloklar Çok Fazlı FFT Çekirdeği,

bulunurlar. CFIR süzgeçlerin arkasına, hayli azalmış olan Örtüştürme ve

örnek hızının getirdiği kolaylıktan da yararlanılarak yüksek Anahtarlama Matrisi ve Çok Kanallı DDC bloğudur. + Toplama

f s 2 katsayılı, keskin birer PFIR (‘Programmable FIR’, Kanallaştırmanın en önemli kısmı çok fazlı FFT

Ayarlanabilir Süzgeç) konulabilir. Bu adımların sonucunda çekirdeğinde gerçekleştirilir. Kanalları birbirinden ayıracak

ilgilenilen işaret, temel bantta arzu edilen bant genişliği ve olan süzgeç yapısı FFT bloğunun önünde çok fazlı olacak K noktalı FFT

(c) örnek hızı ile elde edilmiş olur. Kanallaştırıcı, basitçe, bu biçimde gerçeklenir. Burada girişteki geniş bantlı işaret eşit

yapının çok sayıda ilklendirilmesiyle elde edilir ve Paralel aralıklı kanallara bölünür ve bu kanallar temel banda Faz

DDC olarak adlandırılır. indirilir. Anahtarlama matrisinde, çok fazlı FFT Düzeltme

çekirdeğinden gelen kanalların belirli bir kısmı seçilerek çok

30,72 MS/s ile örneklenen karmaşık girişten, yine temel kanallı DDC bloğuna aktarılır. Bu son blokta ise ince ayar,

f N ) 2

( s bantta 120 kS/s örnek hızı ve 96 kHz bant genişliği ile arzu süzme ve örnek seyreltme işlemleri gerçekleştirilir. Kanallaştırıcı

edilen işaretin elde edilmesi için tasarlanan örnek DDC Çıkışı

yapısı Şekil 3’te verilmiştir. Toplam örnek seyreltme oranı Çok fazlı FFT çekirdeğinin işleyişi ana hatlarıyla

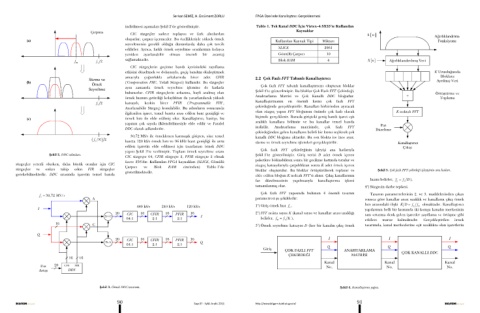

Şekil 2. DDC adımları. Şekil 5’te gösterilmiştir. Giriş verisi D adet örnek içeren

CIC süzgeçte 64, CFIR süzgeçte 2, PFIR süzgeçte 2 olmak

üzere 256’dır. Kullanılan FPGA kaynakları (SLICE, Gömülü paketlere bölündükten sonra bir gecikme hattında tutulur ve

süzgeçler yeterli olurken, daha büyük oranlar için CIC süzgeç katsayılarıyla çarpıldıktan sonra K adet örnek içeren

süzgeçler ve onları takip eden FIR süzgeçler Çarpıcı ve Blok RAM cinsinden) Tablo 1’de bloklar oluşturulur. Bu bloklar örtüştürülerek toplanır ve Şekil 5. Çok fazlı FFT çekirdeği işleyişinin ana hatları.

gerekebilmektedir. DDC sırasında işaretin temel banda gösterilmektedir. elde edilen bloğun K noktalı FFT’si alınır. Çıkış kanallarının

faz düzeltmesinin yapılmasıyla kanallaştırma işlemi hızını belirler, f = f D ),

s

ç

tamamlanmış olur. 4°) Süzgecin darbe tepkesi.

Çok fazlı FFT yapısında bulunan 4 önemli tasarım

f = 30,72 MS s Tasarım parametrelerinin 2. ve 3. maddelerinden çıkan

/

s

A parametresi şu şekildedir: sonuca göre kanallar arası uzaklık ve kanalların çıkış örnek

u

480 kS/s 240 kS/s 120 kS/s 1°) Giriş örnek hızı f , hızı arasındaki ilişki K D = f ç f olmaktadır. Kanallaştırıcı

I s yapılarının belli bir kısmında iki komşu kanalın merkezinin

20 CIC 16 CFIR 16 PFIR 16 2°) FFT nokta sayısı K (kanal sayısı ve kanallar arası uzaklığı tam ortasına denk gelen işaretler zayıflama ve örtüşme gibi

B+C I

64:1 2:1 2:1 belirler, f = f K ), etkilere maruz kalmaktadır. Gerçekleştirilen örnek

u

s

16 C 3°) Örnek seyreltme katsayısı D (her bir kanalın çıkış örnek tasarımda, kanal merkezlerine eşit uzaklıkta olan işaretlerin

Q

20 CIC 16 CFIR 16 PFIR 16 I I I

D–A Q

64:1 2:1 2:1 Q Q Q

Giriş ÇOK FAZLI FFT ANAHTARLAMA

ÇEKİRDEĞİ MATRİSİ ÇOK KANALLI DDC

16 16

Kanal Kanal Kanal

Faz 28 cos sin No. No. No.

Artışı DDS

Şekil 3. Örnek DDC tasarımı. Şekil 4. Kanallaştırıcı yapısı.

90 Sayı 07 · Eylül-Aralık 2011 http://www.bilgem.tubitak.gov.tr/ 91